Qualcomm et Google viennent d'annoncer un mouvement intéressant pour ceux qui s'intéressent aux processeurs et aux jeux d'instructions : une puce compatible RISC-V plutôt qu'ARM, pour les appareils mobiles et plus spécifiquement les montres sous WearOS, le processeur faisant partie de la gamme « Snapdragon Wear ».

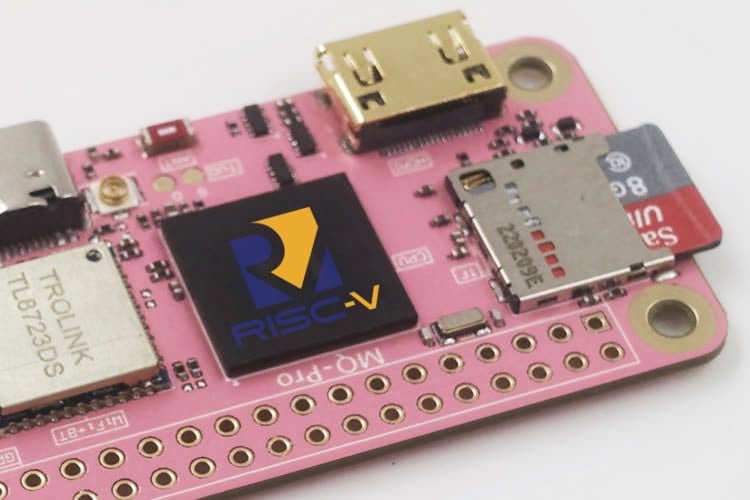

Si vous ne connaissez pas RISC-V, il s'agit d'un jeu d'instructions — l'ensemble des commandes possibles pour un processeur — open source, moderne et efficace. Il est assez récent, mais il entre en confrontation directe avec les puces qui emploient le jeu d'instructions ARM, comme celle d'Apple ou la majorité de celles qui animent les appareils Android (l'OS gère encore le x86, mais ce choix reste assez rare). Avant de continuer, nous vous conseillons d'aller lire notre série sur les puces RISC-V, qui expliquent pourquoi ce jeu d'instructions est important.

La révolution RISC-V : tout ce qu'il faut savoir sur ce jeu d'instructions prometteur

Maintenant, il y a un point intéressant à analyser : la cible. Le monde des « wearables », c'est-à-dire les périphériques portables comme les montres connectées, est un peu particulier. Si nous prenons le système sur puce qui anime la dernière Pixel Watch, il contient quatre cœurs Cortex A53, un CPU basse consommation plutôt ancien. Et dans la puce en question, il est gravé en 4 nm, pour tenter de réduire au maximum sa consommation. Dans la gamme d'Arm, il s'agit d'une vieille puce — elle date de 2012 — qui a déjà été remplacée par le Cortex A55 puis — plus récemment — par le Cortex A510. Et c'est donc l'adversaire parfait pour les premières puces RISC-V : un vieux composant, lent et daté. Car c'est tout le problème des CPU RISC-V actuels : ils consomment très peu, certes, mais offrent des performances faibles.

Ce passage à RISC-V pour ce type de gamme est d'ailleurs dans un sens un aveu d'échec pour ARM : le simple fait de voir une puce de 2012 dans ce domaine montre que la gamme basse consommation d'ARM a un problème1. C'est d'ailleurs à peu près généralisé : AMD et Intel, par exemple, n'ont jamais réussi à proposer des cœurs basse consommation vraiment convaincant, entre le Jaguar d'AMD qui a plombé les performances des PlayStation 4 et Xbox One, et les Atom qu'Intel n'a pas réussi à imposer dans les smartphones et a été recyclé comme cœur annexe. C'est peut-être d'ailleurs un des vrais points forts d'Apple, souvent sous-estimé : les cœurs basse consommation des puces A et M sont bien plus performants que ceux de la concurrence.

Et ce point est probablement lié à une chose : Apple avait besoin d'une montre réactive. La différence entre l'Apple Watch S3 (équipée de cœurs Cortex A7, le prédécesseur du Cortex A53) et l'Apple Watch S4 (qui récupère les cœurs basse consommation des puces d'iPhone) est d'ailleurs édifiante sur ce point.

C'est ici que ça devient intéressant, en réalité : comme l'offre d'Arm n'est pas totalement adaptée aux usages, Qualcomm a fait un choix pragmatique. Au lieu de développer un CPU compatible avec le jeu d'instructions ARM pour cet usage (ce que la société est capable de faire), c'est un CPU compatible RISC-V qui va être proposé, sans que l'on sache si c'est une version maison ou un cœur disponible sur le marché. Les raisons sont probablement financières, mais ça ne change rien au résultat : RISC-V pourrait attaquer la concurrence par le bas, avec une montée en performances dans le temps, spécialement si Arm (la société) resserre la vis sur les licences.

-

Il faut nuancer un point : la gamme basse consommation est globalement efficace dans un smartphone pour effectuer les tâches secondaires. Mais pour une montre connectée ou un appareil où ce type de CPU est le maître d'œuvre, c'est une autre histoire. ↩︎